That's a lot of buzzwords! I assume you already know that SerDes stands for serializer-deserializer. It is an IP block that takes parallel data from buses on the chip and transforms it into a very high-frequency serial signal. In this case, the signal is 112 billion cycles per second, or 112G. The deserializer does the opposite, receiving a very fast signal on a single pin, and transforming it into parallel data on the chip. The transmission (serializer) side is the simpler of the two. The big complexity on the receive side is that there is no explicit clock, it has to be recreated from the data. Since there may be a lot of distortion on the channel (the electrical connection between the serializer on one chip and the deserializer on the other (or to the optical converter) aggressive equalization is required. If you actually see the signal before equalization, it seems amazing that this approach actually works.

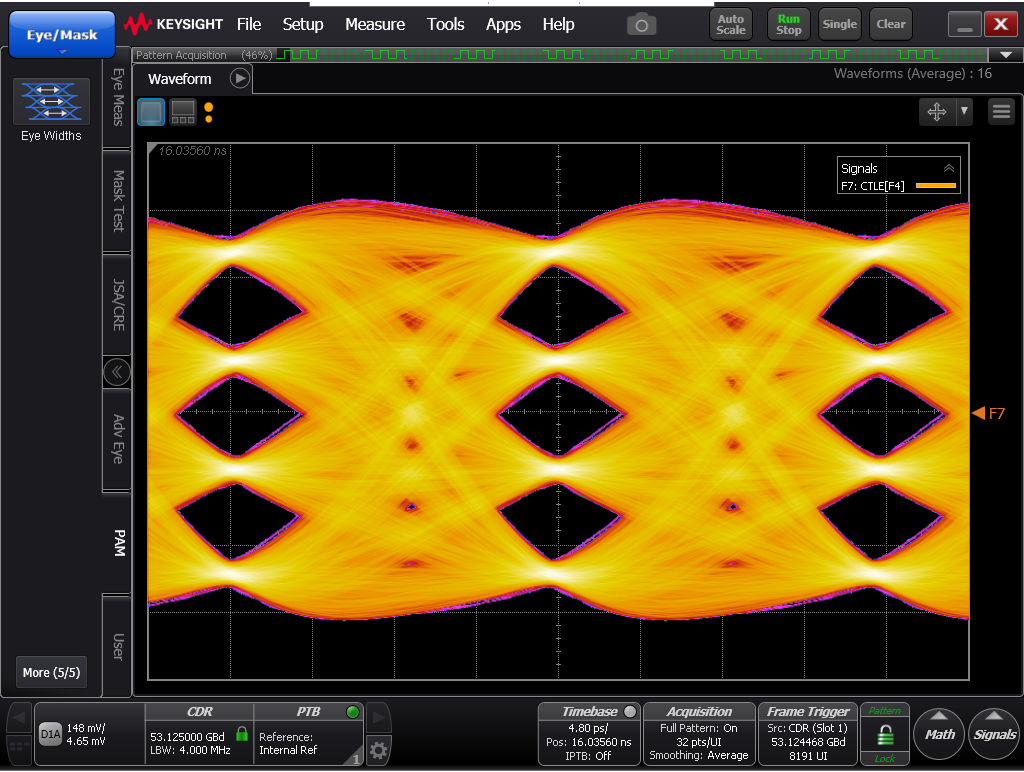

At 112G, it is no longer possible to use a simple NRZ signaling system, where the bits are truly serial as described in the paragraph above. The signaling system, PAM4, has two bits per clock cycle, so the requirements for recovering the clock and the data are even more challenging since there are three eyes, as shown in the above image. The PHY is the part of the design that actually attached to the signal lines. Whereas most of the SerDes is digital and largely or completely independent of the process node, the PHY is different for every manufacturer and every node. I said that you can't use NRZ at 112G, and that is true, but the interface is backward compatible with lower-performance interfaces which do use NRZ.

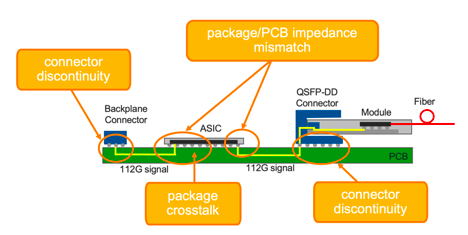

ELR stands for extended long reach. Details of the design of the PHY, in particular, depend on the length of the signal line between the two SerDes devices. The longer the line, the more challenging the design. ELR is the longest range and so the most challenging of all. The diagram above shows a typical way it would get used in a system.

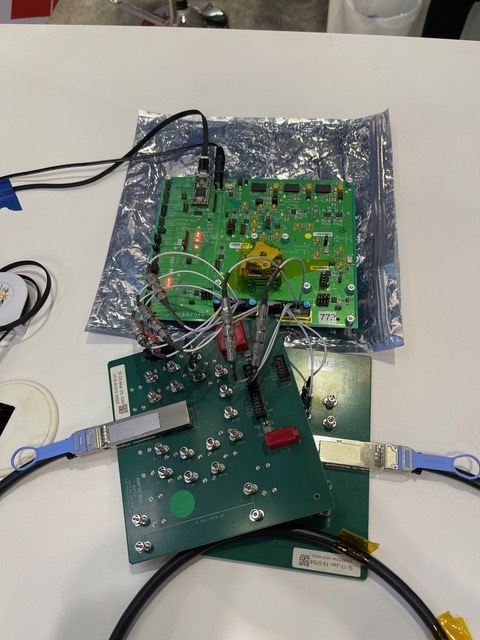

At DesignCon, Cadence demonstrated the system in 4nm. The demonstration board was hooked up to two meters of QFSP copper cable to form the "long reach" since this is just an evaluation board and it is not practical to set up a full system with multiple boards, backplanes, ribbon cables, and the like. QFSP stands for quad small form-factor pluggable, and it is a standard form of cable used to hook up routers and other signaling systems. This demo was in 4nm, as I said, but. the interface is available in 5nm, 6nm, and 7nm, too. One of the key parameters for any interface like this is the bit error rate or BER. For this interface, it is 2e-12.

The Implementation is DSP-based (like all modern high-speed SerDes). To provide unprecedented performance, this SerDes incorporates state-of-the-art DSP approaches such as reflection cancellation and maximum likelihood sequence detection (MLSD).

The Market

So what would you use this IP block for? Networking is the key market driver here. The 112Gbps lane rate has been adopted in 100G/200G/400G Ethernet and leads to 800G Ethernet using 8 lanes of 112G SerDes, as defined by the IEEE 802.3df standard. With the growth in hyperscale data centers, the switch silicon bandwidth doubles every two years. 25.6TB switch products are available in the market, and the next-generation 51.2TB is around the corner. These high bandwidth switches use 112G SerDes as the foundation IP with either 256 or 512 lanes of 112G in the SoCs. In addition to networking, the AI/ML workload with chip-to-chip interconnect between multiple training SoCs demands higher bandwidth using 112G SerDes in advanced process nodes. 5G applications are another strong driver. 56G SerDes has been used for 5G CPRI/eCPRI interfaces and next-generation 5G applications need 112G SerDes to provide higher bandwidth and lower latency.

Other Posts

I've written several posts on various aspects of 112G, from when we first introduced the IP at 7nm, how to do signal integrity, the 5nm implementation (and, of course, today the 4nm implementation).

The Future

The "next" SerDes standard with be 224G (obviously twice 112G). For more about that, see my post DesignCon 2022: The 224G Show. The standard has not been written yet, so obviously IP blocks are not available. As far as I can tell, the signaling approach has not even been decided, with all of PAM-4, PAM-6, PAM-8, and PAM-16 being considered. PAM-16 (4 bits per clock cycle with 15 eyes) seems too much of a stretch to me, but it's not my area of expertise.

Video

Watch as Yang Zhang, the product manager, demonstrates the new PHY at DesignCon earlier this year. The video is less than two minutes so it's a quick watch.

Shenzhen HongYuan Electronics Co.,Ltd

Shenzhen HongYuan Electronics Co.,Ltd